Overview

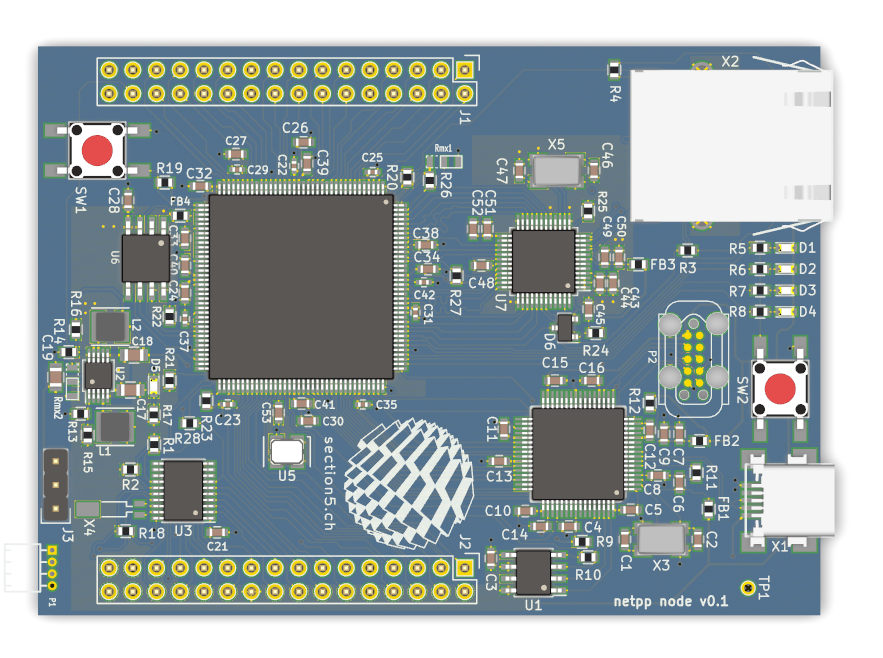

The netpp node is basically a 2(3) chip, simple two layer solution that provides real time networking control and interfacing to custom hardware – the way you want it. Its main engine is a FPGA circuit that is programmed to be a compact microcontroller with specific safety features and configureable interfaces.

Features

- netpp remote control and firmware updates over UDP/IP

- Configureable interfaces: I2C, UART, SPI, proprietary

DataPortvia DMA - Population options with on-board ADC/DAC and real time clock

- In Circuit Emulation on board

- Programmable with GCC

First prototype 2017

[ Link to old page ]

Documentation

[ PDF ]

Firmware images

on request

Measurements

[ Link to old page ]

Public project with demo

[ hackaday ]

History

The netpp node was developed as a concept study for a scalable solution based on programmable hardware that can be described from a functional point of view using XML. The embedded microcontroller core is a stack architecture (a pipelined implementation of Øyvind Harboes ZPU) which allows to add security and safety features in order to fall back to default operation levels in case hardware or software fails.

The high configureability of such a system on chip also introduces maintenance problems: Which version is it, what functionality does it cover, et cetera. This problem is tackled by the built-in netpp feature: Each single device is aware of what it is capable of and can report its features to the client accessing it.

Application scenarios

We use the netpp node mostly in distributed test and measurement scenarios, for instance to measure temperature and gas concentrations and stream the data to a monitor. But by reprogramming it, it can take over just another job. Here are a few examples:

- netpp to multiple RS485 modbus gateway

- LED light stripe animation control: using particular I/O, the CPU can process color animations and drive up to eight WS2812B chains

- remote display interface: Added a specific LCD display to remote-display images over ethernet [ Link ]

- Crypto Token generator: Using a true random seed, challenge/response procedures are generated in hardware with side channel attacks being nearly impossible.

Sustainable technology

The components on the netpp node are old, established technology. In fact, the FPGA will some day reach end of life. What then? Well, there is the next FPGA technology in the pipeline. We can program exact the same CPU and I/O onto the next generation netpp node such that this code may even survive us as developers.

There are a few more benefits of having the entire source of hardware and software under one hood:

- We can simulate the entire system on chip against external stimuli, meaning, we can build a digital twin of this system that is entirely virtual and where its ‘pins’ can be driven through a Python Script by anyone without further programming knowledge

- We can translate or port the entire code easily to a new platform, without the customer application changing. The timing is exactly the same.